# **Chapter 3**

# Logic and Fault Simulation

**VLSI Test Principles and Architectures**

# **About the Chapter**

- Circuit simulation models

- □ Logic simulation techniques

- Fault simulation techniques

# **Logic and Fault Simulation**

### □ Introduction

- Simulation models

- □ Logic simulation

- Fault simulation

- Concluding remarks

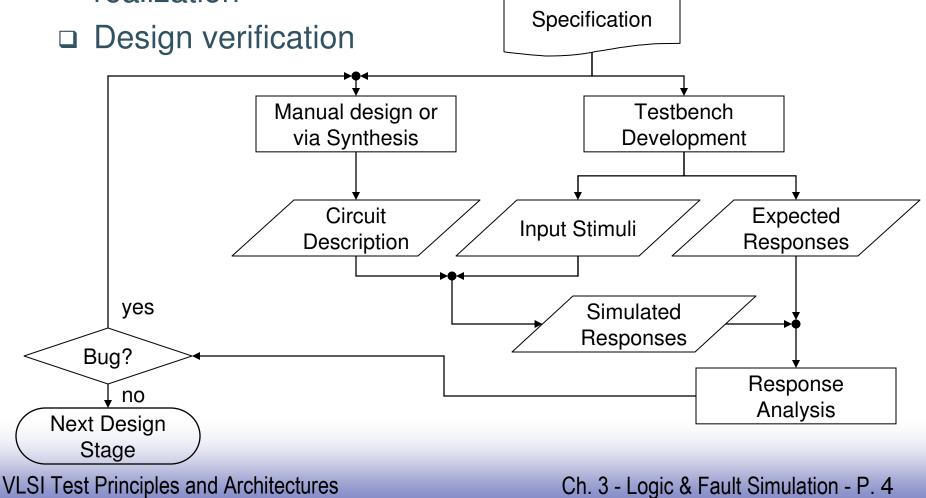

# **Logic Simulation**

Predict the behavior of a design prior to its physical realization

### **Fault Simulation**

Predicts the behavior of faulty circuits

- As a consequence of inevitable fabrication process imperfections

- An important tool for test and diagnosis

- Estimate fault coverage

- Fault simulator

- Test compaction

- Fault diagnosis

# **Logic and Fault Simulation**

- Introduction

- □ Simulation models

- □ Logic simulation

- Fault simulation

- Concluding remarks

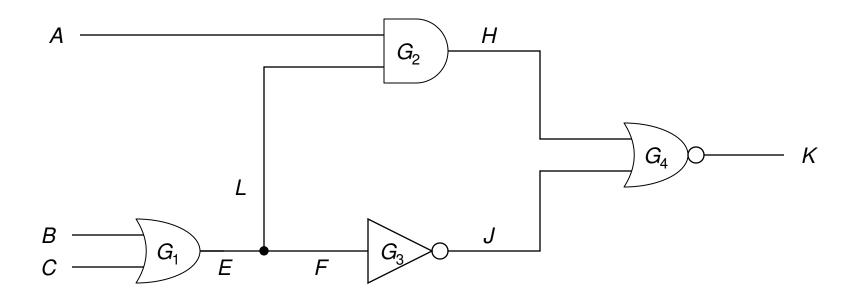

### **Gate-Level Network**

#### □ The interconnections of logic gates

#### **VLSI Test Principles and Architectures**

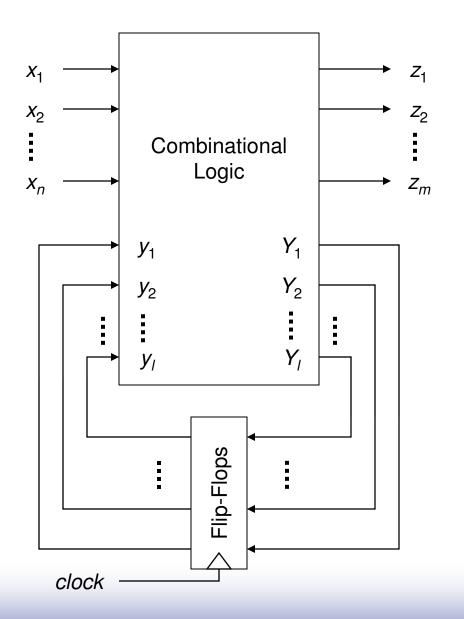

# **Sequential Circuits**

The outputs depend on both the current and past input values

*x<sub>i</sub>*: primary input (PI)

*z<sub>i</sub>*: primary output (PO)

*y<sub>i</sub>*: pseudo primary input (PPI)

Y<sub>i</sub>: pseudo primary output (PPO)

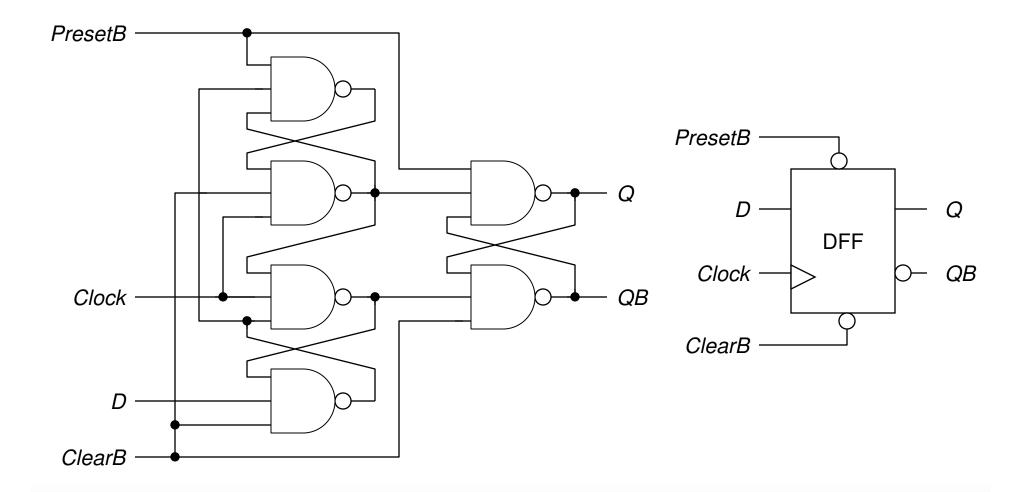

# A Positive Edge-Triggered D-FF

# **Logic Symbols**

# The most commonly used are 0, 1, *u* and *Z*1 and 0

true and false of the two-value Boolean algebra

Unknown logic state (maybe 1 or 0)

- High-impedance state

- Not connected to V<sub>dd</sub> or ground

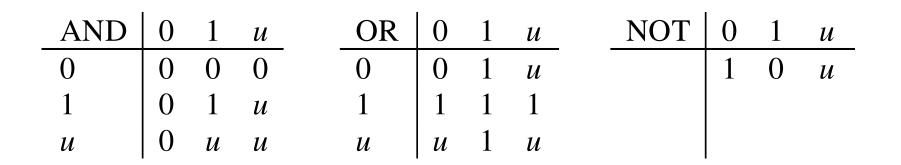

# **Ternary Logic**

#### □ Three logic symbols: 0, 1, and *u*

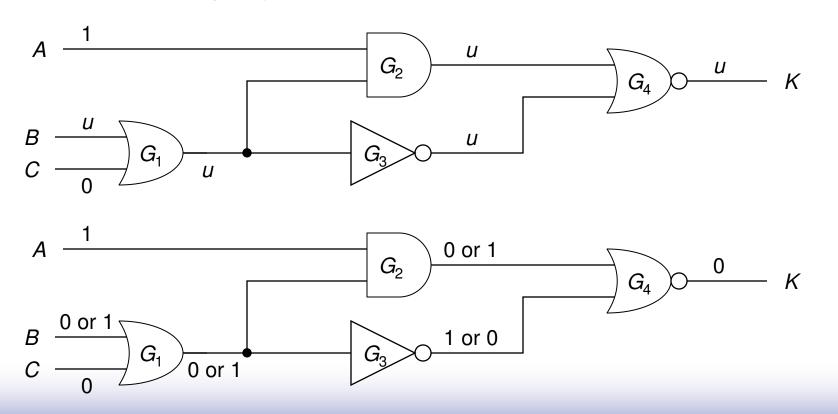

# **Information Loss of Ternary Logic**

- □ Simulation based on ternary logic is pessimistic

- A signal may be reported as unknown when its value can be uniquely determined as 0 or 1

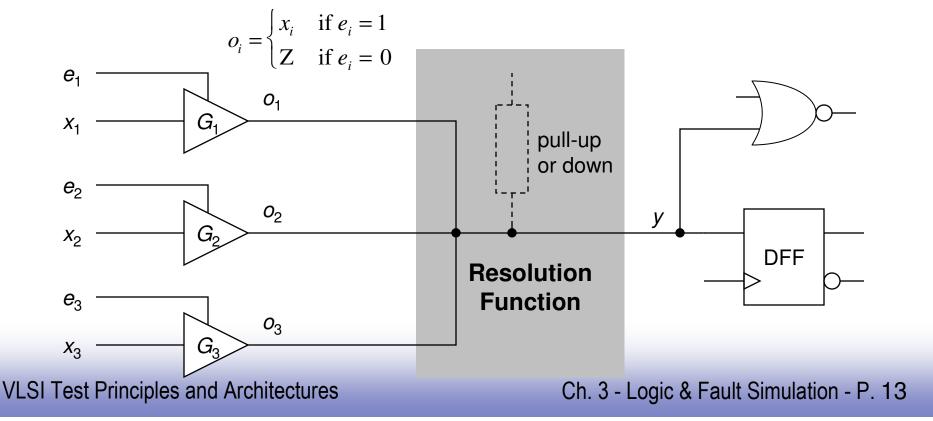

# **High-Impedance State Z**

- Tri-state gates permit several gates to time-share a common wire, called bus

- A signal is in high-impedance state if it is connected to neither V<sub>dd</sub> nor ground

# **Resolving Bus Conflict**

- Bus conflict occurs if at least two drivers drive the bus to opposite binary values

- To simulate tri-state bus behavior, one may insert a resolution function for each bus wire

- May report only the occurrence of bus conflict

- May utilize multi-valued logic to represent intermediate logic states (including logic signal values and strengths)

# **Logic Element Evaluation Methods**

□ Choice of evaluation technique depends on

- Considered logic symbols

- Types and models of logic elements

- Commonly used approaches

- Truth table based

- Input scanning

- Input counting

- Parallel gate evaluation

# **Truth Table Based Gate Evaluation**

- The most straightforward and easy to implement

- For binary logic, 2<sup>n</sup> entries for n-input logic element

- May use the input value as table index

- Table size increases exponentially with the number of inputs

- Could be inefficient for multi-valued logic

- A k-symbol logic system requires a table of 2<sup>mn</sup> entries for an n-input logic element

- $-m = \lceil \log_2 k \rceil$

- Table indexed by *mn*-bit words

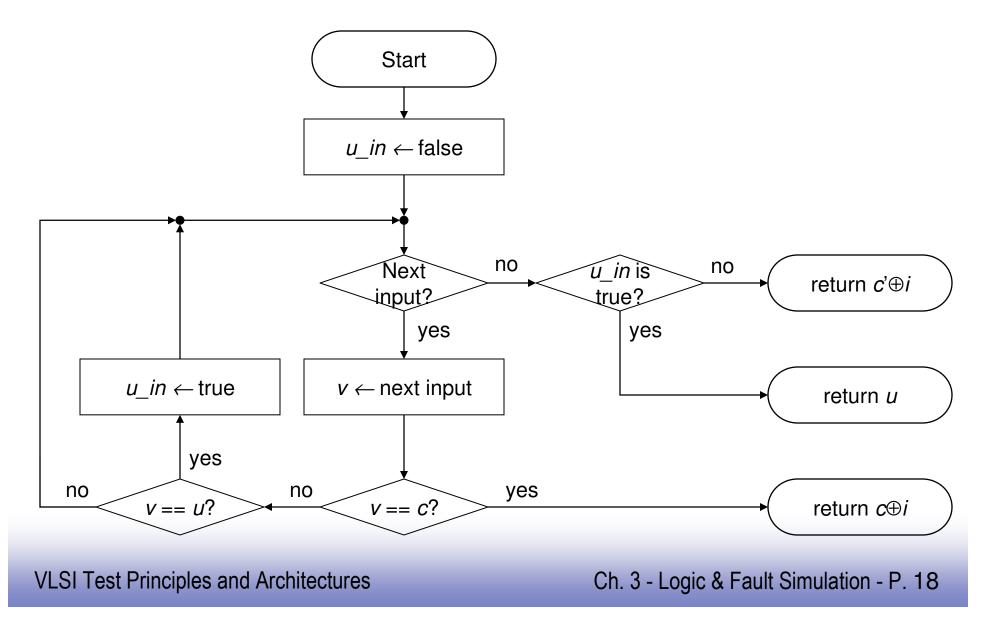

# **Input Scanning**

- The gate output can be determined by the types of inputs

- If any of the inputs is the controlling value, the gate output is c⊕i

- Otherwise, if any of the inputs is u, the gate output is u

- Otherwise, the gate output is  $c' \oplus i$

| Table 3.2: The c (controlling) andi (inversion) values of basic gates |                                          |          |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------|------------------------------------------|----------|--|--|--|--|--|--|--|

|                                                                       |                                          |          |  |  |  |  |  |  |  |

|                                                                       | C                                        | <u>l</u> |  |  |  |  |  |  |  |

| AND                                                                   | 0                                        | 0        |  |  |  |  |  |  |  |

| OR                                                                    | 1                                        | 0        |  |  |  |  |  |  |  |

| NAND                                                                  | 0                                        | 1        |  |  |  |  |  |  |  |

| NOR                                                                   | 1                                        | 1        |  |  |  |  |  |  |  |

| LSI Test Principles and Architectures                                 | Ch. 3 - Logic & Fault Simulation - P. 17 |          |  |  |  |  |  |  |  |

# Input Scanning - cont'd

# **Input Counting**

- Keep the counts of controlling and unknown inputs

- *c\_count*: the number of controlling inputs

- *u\_count*: the number of unknown inputs

- Update counts during logic simulation

- Example:

One input of a NAND switches from 0 to u

- *c\_count* --

- *u\_count* ++

- Same rules as input scanning used to evaluate gate outputs

### **Parallel Gate Evaluation**

#### □ Exploit the inherent concurrency in the host computer

A 32-bit computer can perform 32 logic operations in parallel

Ch. 3 - Logic & Fault Simulation - P. 20

# **Multi-Valued Parallel Gate Evaluation**

□ Use ternary logic as example

- Assume

- w-bit wide word

- Symbol encoding:  $v_0 = (00), v_1 = (11), v_u = (01)$

- Associate with each signal X two words,  $X_1$  and  $X_2$

- $-X_1$  stores the first bits and  $X_2$  the second bits of the *w* copies of the same signal

- AND and OR operations are realized by applying the same bitwise operations to both words

$- C = OR(A,B) = > C_1 = OR(A_1,B_1) \text{ and } C_2 = OR(A_2,B_2)$

Complement requires inversion

- C = NOT(A) ==> C<sub>1</sub> = NOT(A<sub>2</sub>) and C<sub>2</sub> = NOT(A<sub>1</sub>)

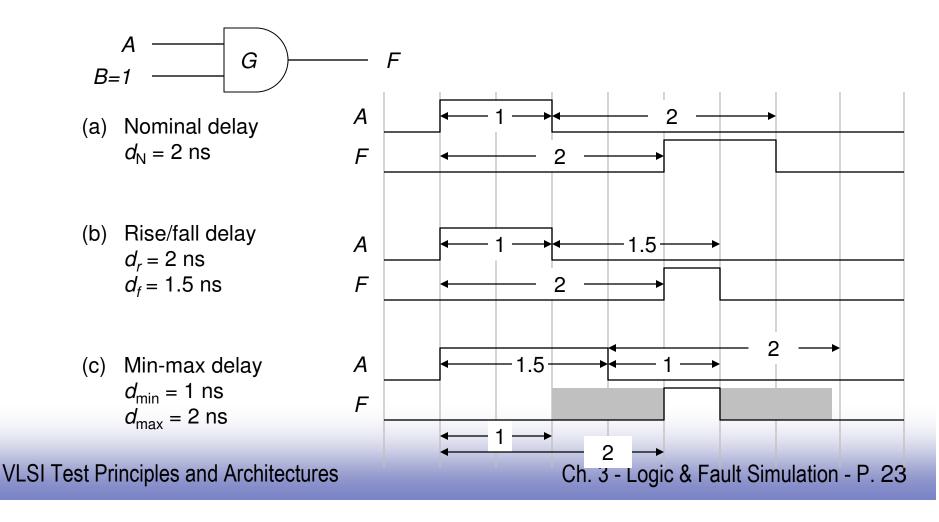

# **Timing Models**

- Transport delay

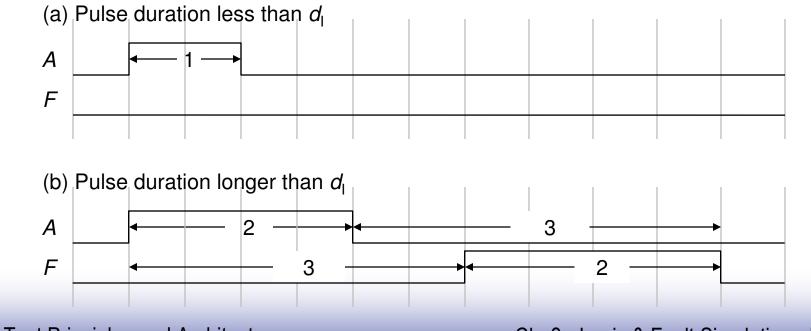

- Inertial delay

- □ Wire delay

- Function element delay model

# **Transport Delay**

The time duration it takes for the effect of gate input changes to appear at gate outputs

# **Inertial Delay**

The minimum input pulse duration necessary for the output to switch states

$$\begin{array}{c|c} A & \hline \\ B=1 & \hline \\ \end{array} \quad F \quad d_{\rm I} = 1.5 \text{ ns}, \ d_{\rm N} = 3 \text{ ns} \end{array}$$

VLSI Test Principles and Architectures

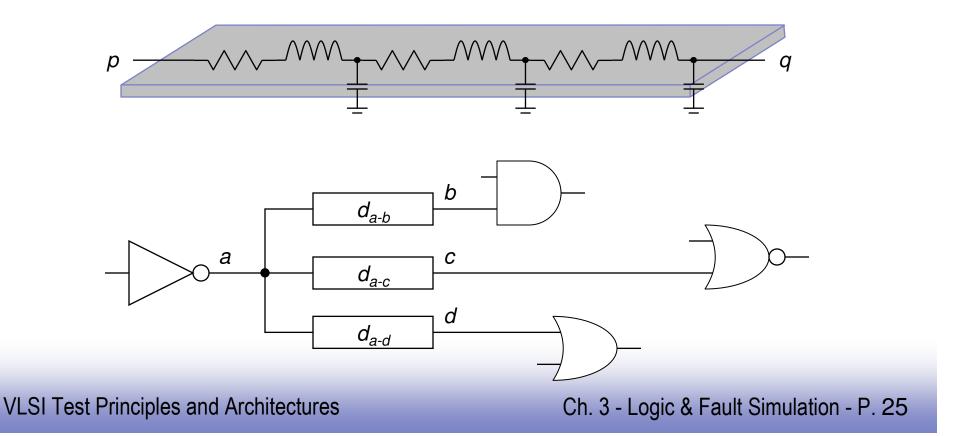

# Wire Delay

- □ Wires are inherently resistive and capacitive

- It takes finite time for a signal to propagate along a wire

# **Functional Element Delay Model**

#### For more complicated functional elements like flipflops

| Input condition         |            |                | Present<br>state | Outputs |              | Delays (ns)   |      |       |                      |  |  |

|-------------------------|------------|----------------|------------------|---------|--------------|---------------|------|-------|----------------------|--|--|

| D                       | Clock      | <b>PresetB</b> | ClearB           | q       | Q            | QB            | to Q | to QB | Comments             |  |  |

| X                       | X          | $\downarrow$   | 0                | 0       | $\uparrow$   | $\rightarrow$ | 1.6  | 1.8   | Asynchronous preset  |  |  |

| X                       | X          | 0              | $\downarrow$     | 1       | $\downarrow$ | $\uparrow$    | 1.8  | 1.6   | Asynchronous clear   |  |  |

| 1                       | $\uparrow$ | 0              | 0                | 0       | $\uparrow$   | $\downarrow$  | 2    | 3     | $Q: 0 \rightarrow 1$ |  |  |

| 0                       | $\uparrow$ | 0              | 0                | 1       | $\downarrow$ | $\uparrow$    | 3    | 2     | $Q: 1 \rightarrow 0$ |  |  |

| X Š indicates donÕtcare |            |                |                  |         |              |               |      |       |                      |  |  |

Table 3.3:

The D flip-flop I/O delay model

# **Logic and Fault Simulation**

- Introduction

- Simulation models

- □ Logic simulation

- Fault simulation

- Concluding remarks

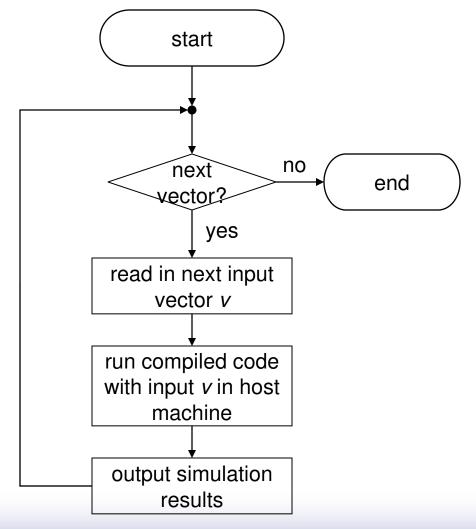

### **Compiled Code Simulation**

Translate the logic

network into a series of

machine instructions that

model the gate functions

and interconnections

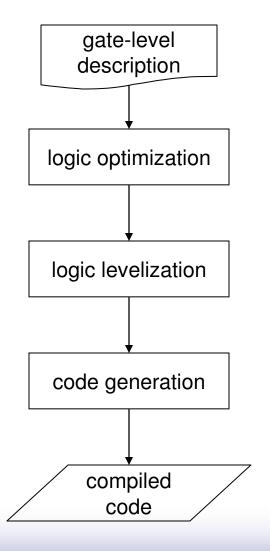

### **Compiled Code Generation Flow**

#### **VLSI Test Principles and Architectures**

Ch. 3 - Logic & Fault Simulation - P. 29

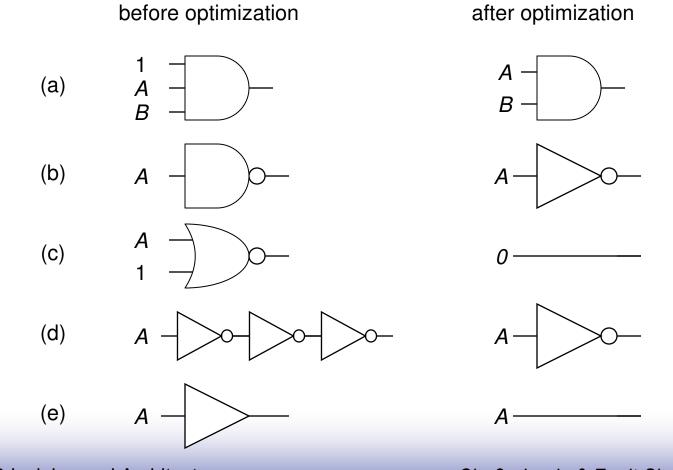

# **Logic Optimization**

#### □ Enhance the simulation efficiency

**VLSI Test Principles and Architectures**

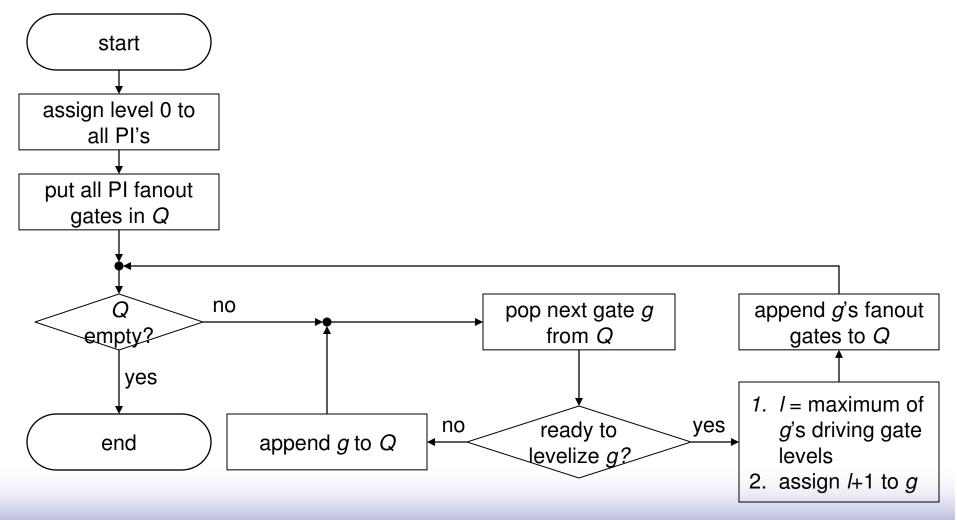

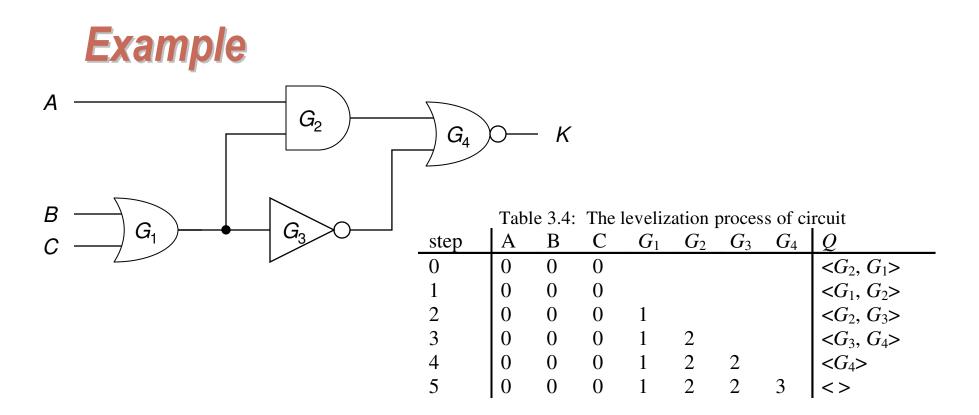

# **Logic Levelization**

Determine the order of gate evaluations

**VLSI Test Principles and Architectures**

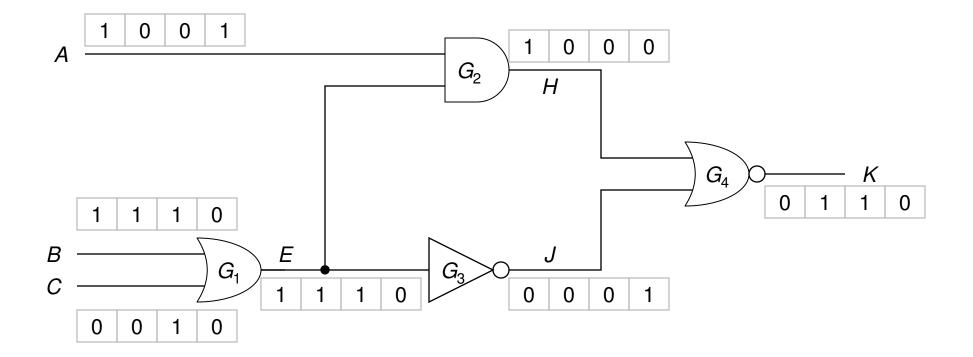

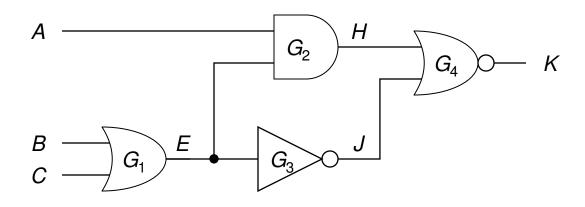

□ The following orders are produced

- $G_1 \implies G_2 \implies G_3 \implies G_4$

- $G_1 \implies G_3 \implies G_2 \implies G_4$

# **Code Generation**

# High-level programming language source code

- Easier to debug

- Can be ported to any target machine that has the compiler

- Limited in applications due to long compilation times

- Native machine code

- Generate the target machine code directly

- Higher simulation efficiency

- Not as portable

# **Code Generation - cont'd**

#### □ Interpreted code

- The target machine is a software emulator

- The codes are interpreted and executed one at a time

- Best portability and maintainability

- Reduced performance

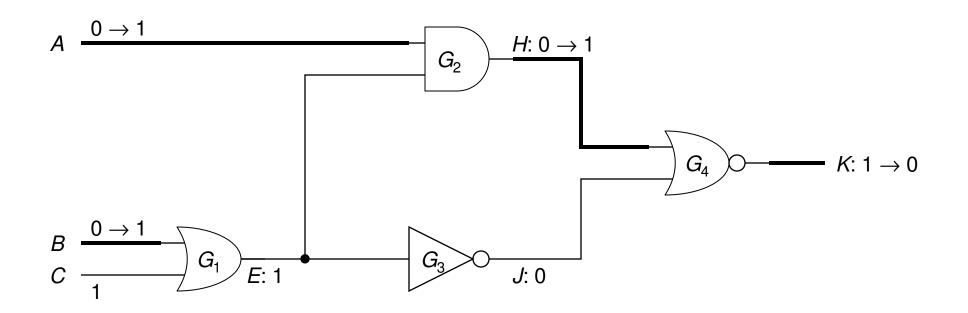

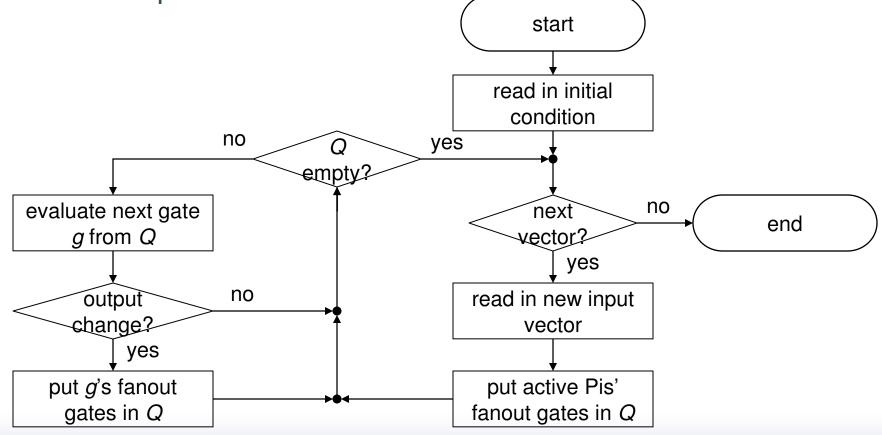

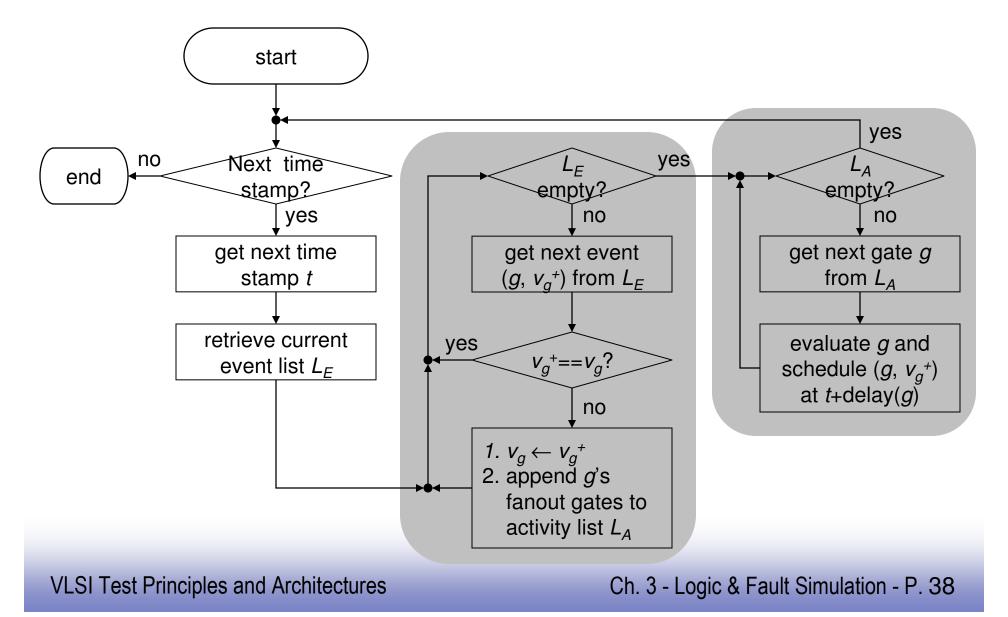

### **Event-Driven Simulation**

- □ Event: the switching of a signal's value

- An event-driven simulator monitors the occurrences of events to determine which gates to evaluate

Ch. 3 - Logic & Fault Simulation - P. 35

# **Zero-Delay Event-Driven Simulation**

□ Gates with events at their inputs are places in the event queue *Q*

**VLSI Test Principles and Architectures**

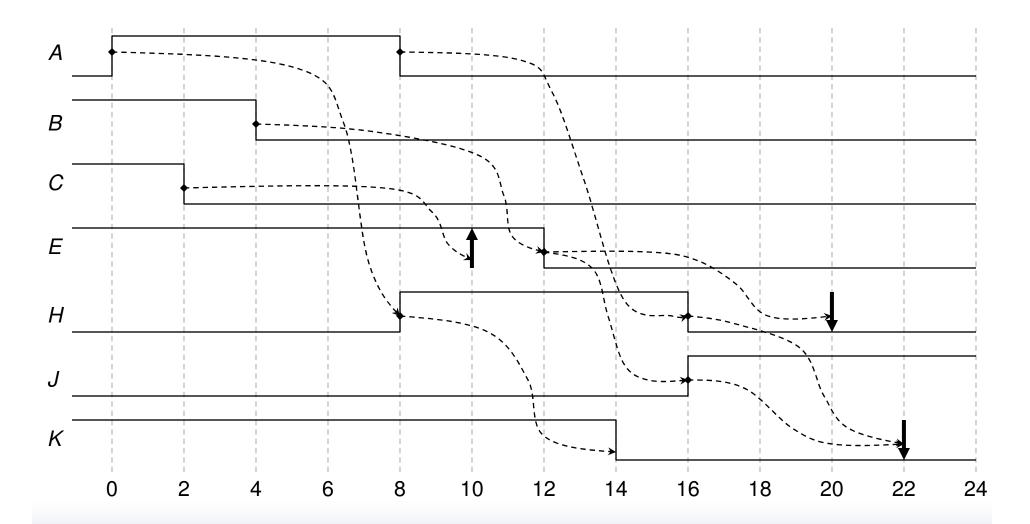

### **Nominal-Delay Event-Driven Simulation**

□ Need a smarter scheduler than the event queue

Not only which gates but also when to evaluate

**VLSI Test Principles and Architectures**

#### **Two-Pass Event-Driven Simulation**

### **Example**

Table 3.5: Two-pass event-driven simulationme $L_E$  $L_A$ Scheduled events

| Time | $L_E$             | $L_A$            | Scheduled events        |

|------|-------------------|------------------|-------------------------|

| 0    | $\{(A,1)\}$       | $\{G_2\}$        | ${(H,1,8)}$             |

| 2    | $\{(C,0)\}$       | $\{G_1\}$        | $\{(E,1,10)\}$          |

| 4    | $\{(B,0)\}$       | $\{G_1\}$        | $\{(E,0,12)\}$          |

| 8    | $\{(A,0),(H,1)\}$ | $\{G_2, G_4\}$   | $\{(H,0,16),(K,0,14)\}$ |

| 10   | $\{(E,1)\}$       |                  |                         |

| 12   | $\{(E,0)\}$       | $\{ G_2, G_3 \}$ | $\{(H,0,20),(J,1,16)\}$ |

| 14   | $\{(K,0)\}$       |                  |                         |

| 16   | $\{(H,0),(J,1)\}$ | $\{G_4\}$        | $\{(K,0,22)\}$          |

| 20   | ${(H,0)}$         |                  |                         |

| 22   | $\{(K,0)\}$       |                  |                         |

**VLSI Test Principles and Architectures**

#### **VLSI Test Principles and Architectures**

## **Compiled-Code vs. Event-Driven Simulation**

#### □ Compiled-code

- Cycle-based simulation

- High switching activity circuits

- Parallel simulation

- Limited by compilation times

#### Event-driven

- Implementing gate delays and detecting hazards

- Low switching activity circuits

- More complicated memory management

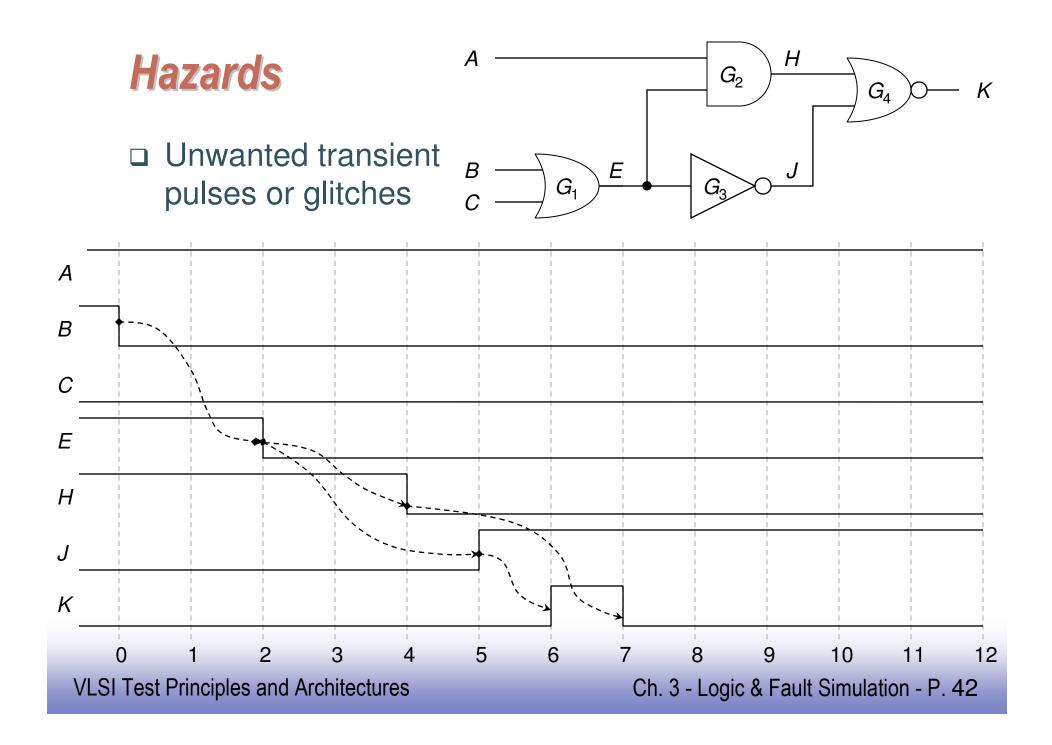

#### □ Static or dynamic

- A static hazard refers to the transient pulse on a signal line whose static value does not change

- A dynamic hazard refers to the transient pulse during a 0-to-1 or 1-to-0 transition

#### □ 1 or 0

Static 1-hazard

Static 0-hazard

Dynamic 1-hazard

Dynamic 0-hazard

VLSI Test Principles and Architectures

#### **Static Hazard Detection**

- □ Let  $V^1 = v_1^1 v_2^1 \cdots v_n^1$  and  $V^2 = v_1^2 v_2^2 \cdots v_n^2$  be two consecutive input vectors

- □ Add a new vector  $V^+ = v_1^+ v_2^+ \cdots v_n^+$  according to the following rule

$$v_{i}^{+} = \begin{cases} v_{i}^{1} & \text{if } v_{i}^{1} = v_{i}^{2} \\ u & \text{if } v_{i}^{1} \neq v_{i}^{2} \end{cases}$$

- Simulate the V<sup>1</sup>V<sup>+</sup>V<sup>2</sup> sequence using ternary logic

- □ Any signal that is 1*u*1 or 0*u*0 indicates the possibility of a static hazard.

### **Multi-Valued Logic for Hazard Detection**

G-valued logic for static hazard detection

- □ 8-valued logic for dynamic hazard detection

- Worst case analysis

| Symbol | Interpretation   | 6-valued logic    | 8-valued logic        |

|--------|------------------|-------------------|-----------------------|

| 0      | Static 0         | {000}             | {0000}                |

| 1      | Static 1         | {111}             | {1111}                |

| R      | Rise transition  | $\{001,011\}=0u1$ | {0001,0011,0111}      |

| F      | Fall transition  | $\{100,110\}=1u0$ | {1110,1100,1000}      |

| 0*     | Static 0-hazard  | $\{000,010\}=0u0$ | {0000,0100,0010,0110} |

| 1*     | Static 1-hazard  | $\{111,101\}=1u1$ | {1111,1011,1101,1001} |

| R*     | Dynamic 1-hazard |                   | {0001,0011,0101,0111} |

| F*     | Dynamic 0-hazard |                   | {1000,1010,1100,1110} |

Table 3.6: Multi-valued logic for hazard detection

**VLSI Test Principles and Architectures**

# **Logic and Fault Simulation**

- Introduction

- Simulation models

- Logic simulation

- □ Fault simulation

- Concluding remarks

## **Fault Simulation**

- Introduction

- Serial Fault Simulation

- Parallel Fault Simulation

- Deductive Fault Simulation

- Concurrent Fault Simulation

- Differential Fault Simulation

- Fault Detection

- Comparison of Fault Simulation Techniques

- Alternative to Fault Simulation

- □ Conclusion

#### Introduction

#### □ What is fault simulation?

- Given

- A circuit

- A set of test patterns

- A fault model

- Determine

- Faulty outputs

- Undetected faults

- Fault coverage

## **Time Complexity**

Proportional to

- *n*: Circuit size, number of logic gates

- *p*: Number of test patterns

- f: Number of modeled faults

Since f is roughly proportional to n, the overall time complexity is O(pn<sup>2</sup>)

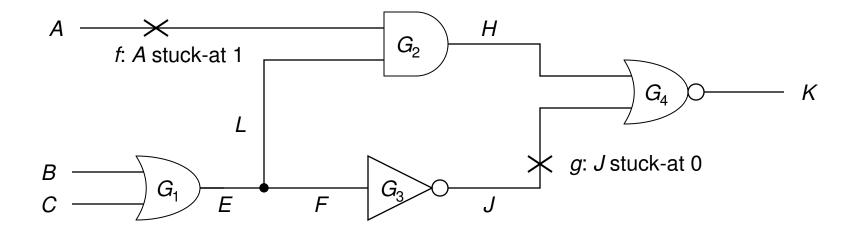

### **Serial Fault Simulation**

First, perform fault-free logic simulation on the original circuit

Good (fault-free) response

For each fault, perform fault injection and logic simulation

• *Faulty* circuit response

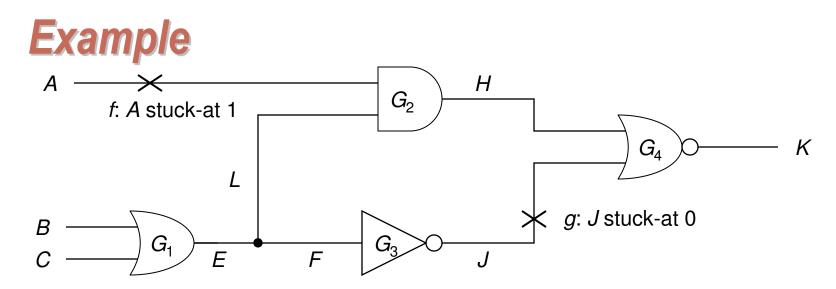

#### Example

| Pat. #    | Input |   |   |   | Iı | nternal | Output |   |       |                |    |

|-----------|-------|---|---|---|----|---------|--------|---|-------|----------------|----|

|           | A     | B | С | E | F  | L       | J      | H | Kgood | K <sub>f</sub> | Kg |

| <i>P1</i> | 0     | 1 | 0 | 1 | 1  | 1       | 0      | 0 | 1     | 0              | 1  |

| P2        | 0     | 0 | 1 | 1 | 1  | 1       | 0      | 0 | 1     | 0              | 1  |

| Р3        | 1     | 0 | 0 | 0 | 0  | 0       | 1      | 0 | 0     | 0              | 1  |

# Fault Dropping

Halting simulation of the detected fault

#### Example

- Suppose we are to simulate P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub> in order

- Fault f is detected by P<sub>1</sub>

- Do not simulate f for P<sub>2</sub>, P<sub>3</sub>

- □ For fault grading

- Most faults are detected after relatively few test patterns have been applied

- For fault diagnosis

- Avoided to obtain the entire fault simulation results

#### **Pro and Con**

Advantages

- Easy to implement

- Ability to handle a wide range of fault models (stuck-at, delay, Br, ...)

- Disadvantages

- Very slow

### **Parallel Fault Simulation**

- Exploit the inherent parallelism of bitwise operations

- □ Parallel fault simulation [Seshu 1965]

- Parallel in faults

- Parallel pattern fault simulation [Waicukauski 1986]

- Parallel in patterns

### **Parallel Fault Simulation**

- □ Assumption

- Use binary logic: one bit is enough to store logic signal

- Use w-bit wide data word

- Parallel simulation

- *w*-1 bit for faulty circuits

- 1 bit for fault-free circuit

Process faulty and fault-free circuit in parallel using bitwise logic operations

**VLSI Test Principles and Architectures**

### Example

| Pat #                 | Input |   |         |   |   | Internal |   |   |   |         |   | Output |

|-----------------------|-------|---|---------|---|---|----------|---|---|---|---------|---|--------|

|                       |       | A | $A_{f}$ | B | С | E        | F | L | J | $J_{g}$ | H | K      |

|                       | FF    | 0 | 0       | 1 | 0 | 1        | 1 | 1 | 0 | 0       | 0 | 1      |

| <b>P</b> <sub>1</sub> | f     | 0 | 1       | 1 | 0 | 1        | 1 | 1 | 0 | 0       | 1 | 0      |

|                       | g     | 0 | 0       | 1 | 0 | 1        | 1 | 1 | 0 | 0       | 0 | 1      |

|                       | FF    | 0 | 0       | 0 | 1 | 1        | 1 | 1 | 0 | 0       | 0 | 1      |

| <b>P</b> <sub>2</sub> | f     | 0 | 1       | 0 | 1 | 1        | 1 | 1 | 0 | 0       | 1 | 0      |

|                       | сŋ    | 0 | 0       | 0 | 1 | 1        | 1 | 1 | 0 | 0       | 0 | 1      |

|                       | FF    | 1 | 1       | 0 | 0 | 0        | 0 | 0 | 1 | 1       | 0 | 0      |

| <b>P</b> <sub>3</sub> | f     | 1 | 1       | 0 | 0 | 0        | 0 | 0 | 1 | 1       | 0 | 0      |

|                       | g     | 1 | 1       | 0 | 0 | 0        | 0 | 0 | 1 | 0       | 0 | 1      |

VLSI Test Principles and Architectures

#### **Pro and Con**

#### Advantages

- A large number of faults are detected by each pattern when simulating the beginning of test sequence

- Disadvantages

- Only applicable to the unit or zero delay models

- Faults cannot be dropped unless all (w-1) faults are detected

### **Parallel Pattern Fault Simulation**

- Parallel pattern single fault propagation (PPSFP)

- Parallel pattern

- With a *w*-bit data width, *w* test patterns are packed into a word and simulated for the fault-free or faulty circuit

- □ Single fault

- First, fault-free simulation

- Next, for each fault, fault injection and faulty circuit simulation

|               |                       | Inj | put |   |   | Output |   |   |   |   |

|---------------|-----------------------|-----|-----|---|---|--------|---|---|---|---|

|               |                       | A   | В   | С | E | F      | L | J | Н | K |

|               | <b>P</b> <sub>1</sub> | 0   | 1   | 0 | 1 | 1      | 1 | 0 | 0 | 1 |

| Fault<br>Free | <b>P</b> <sub>2</sub> | 0   | 0   | 1 | 1 | 1      | 1 | 0 | 0 | 1 |

| The           | <b>P</b> <sub>3</sub> | 1   | 0   | 0 | 0 | 0      | 0 | 1 | 0 | 0 |

|               | <b>P</b> <sub>1</sub> | 1   | 1   | 0 | 1 | 1      | 1 | 0 | 1 | 0 |

| f             | <i>P</i> <sub>2</sub> | 1   | 0   | 1 | 1 | 1      | 1 | 0 | 1 | 0 |

|               | <i>P</i> <sub>3</sub> | 1   | 0   | 0 | 0 | 0      | 0 | 1 | 0 | 0 |

| g             | <b>P</b> <sub>1</sub> | 0   | 1   | 0 | 1 | 1      | 1 | 0 | 0 | 1 |

|               | <b>P</b> <sub>2</sub> | 0   | 0   | 1 | 1 | 1      | 1 | 0 | 0 | 1 |

|               | <i>P</i> <sub>3</sub> | 1   | 0   | 0 | 0 | 0      | 0 | 0 | 0 | 1 |

**VLSI Test Principles and Architectures**

#### **Pro and Con**

#### Advantages

- Fault is dropped as soon as detected

- Best for simulating test patterns that come later, where fault dropping rate per pattern is lower

#### Disadvantages

Not suitable for sequential circuits

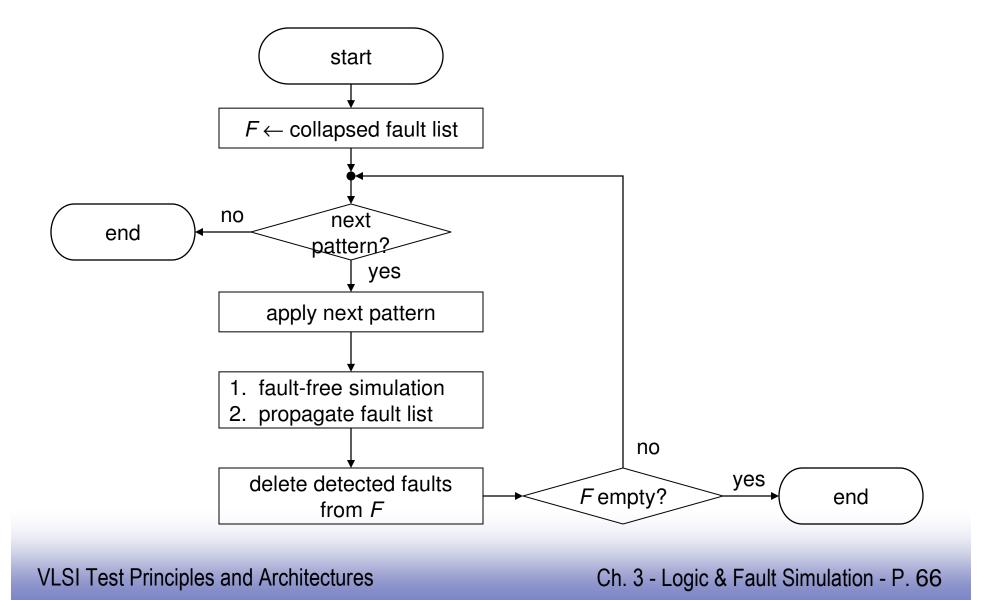

### **Deductive Fault Simulation**

- □ [Armstrong 1972]

- Based on logic reasoning rather than simulation

- $\Box$  Fault list attached with signal *x* denoted as  $L_x$

- Set of faults causing x to differ from its fault-free value

- Fault list propagation

- Derive the fault list of a gate output from those of the gate inputs based on logic reasoning

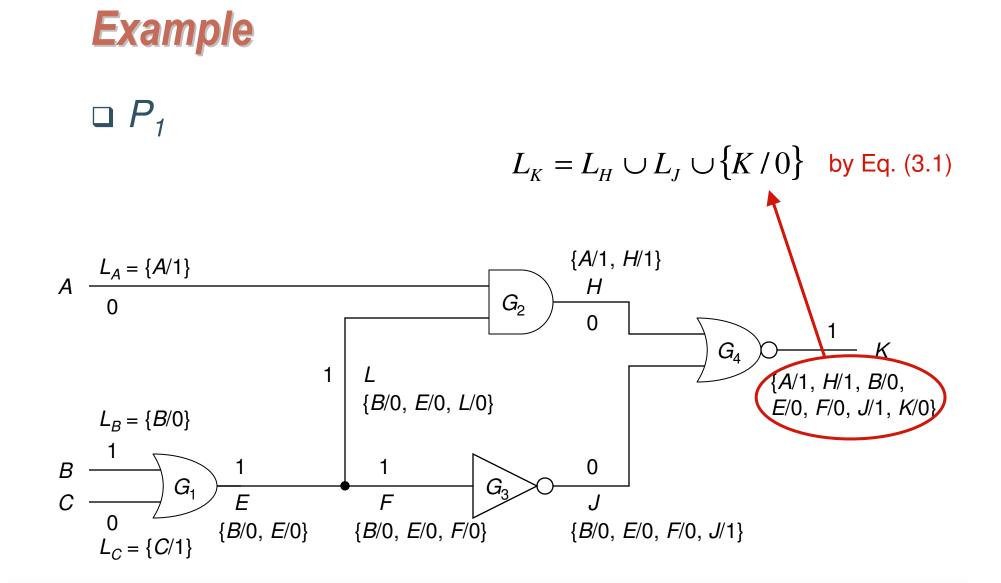

### **Fault List Propagation Rules**

| c : controlling value               |      | с | i |

|-------------------------------------|------|---|---|

| <i>i</i> : inversion value          | AND  | 0 | 0 |

| I : set of gate inputs              | OR   | 1 | 0 |

| z : gate output                     | NAND | 0 | 1 |

| S: inputs holding controlling value | NOR  | 1 | 1 |

□ All gate inputs hold non-controlling value  $L_{z} = \left(\bigcup_{j \in I} L_{j}\right) \cup \left\{\frac{z}{c \oplus i}\right\}$ (3.1)

At least one input holds controlling value

$$L_{z} = \left[\left(\bigcap_{j \in S} L_{j}\right) - \left(\bigcup_{j \in I-S} L_{j}\right)\right] \cup \left\{z/c \oplus i'\right\}$$

(3.2)

**VLSI Test Principles and Architectures**

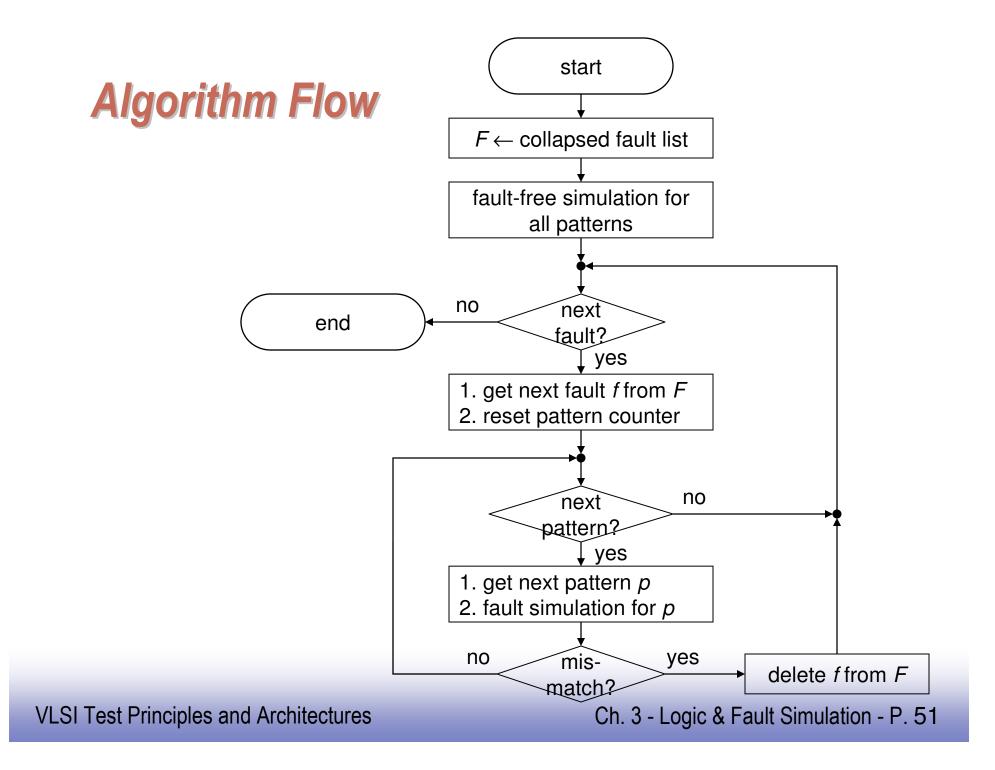

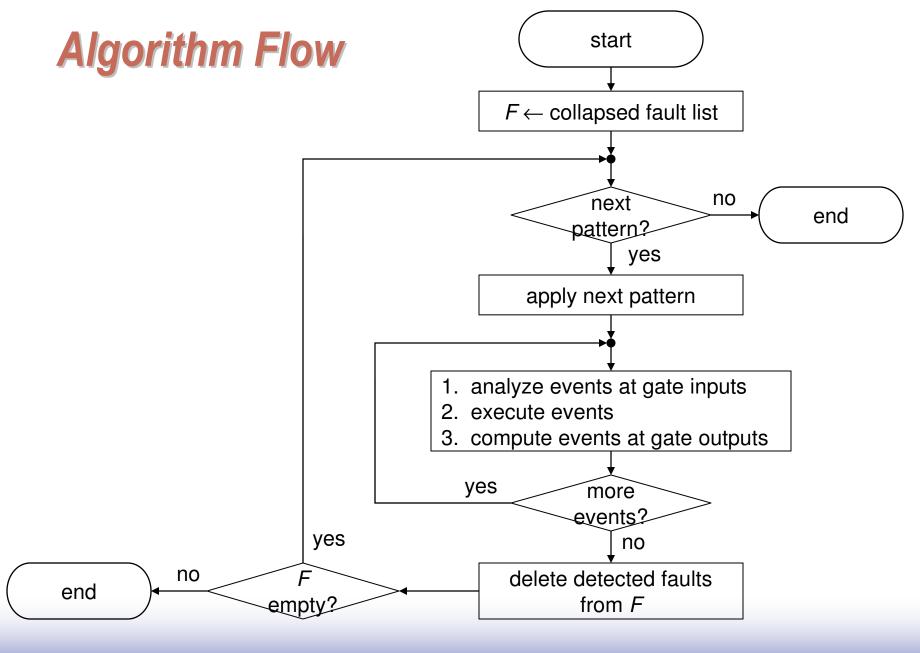

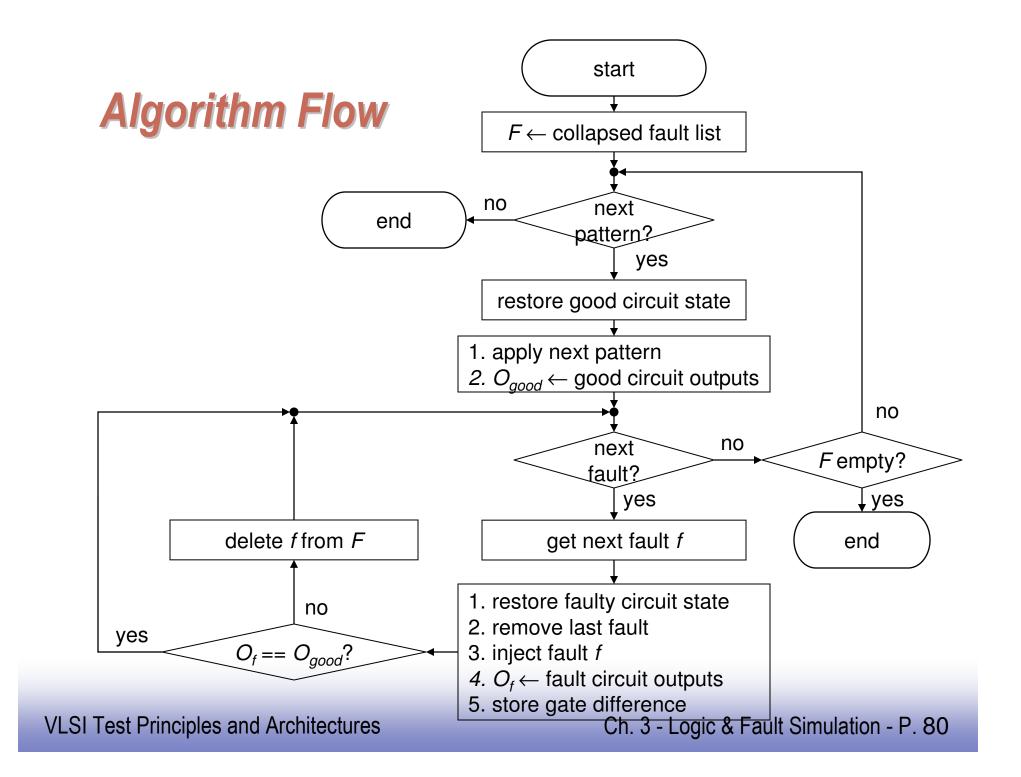

### **Algorithm Flow**

**VLSI Test Principles and Architectures**

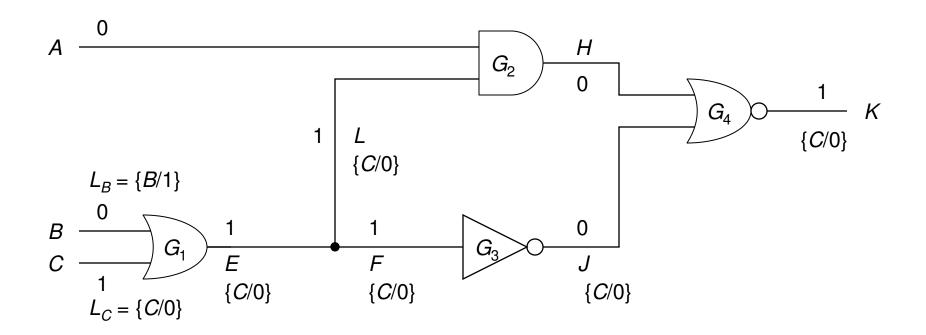

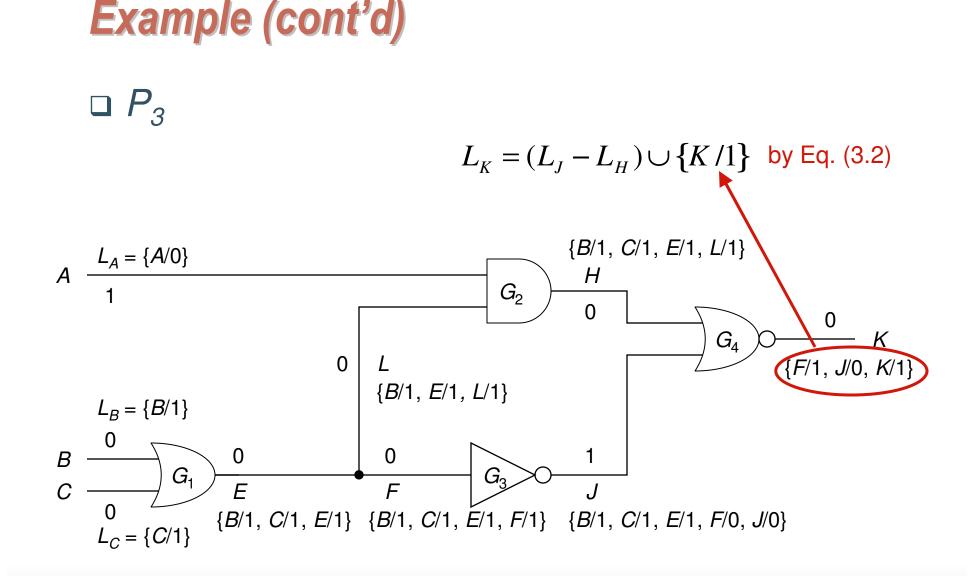

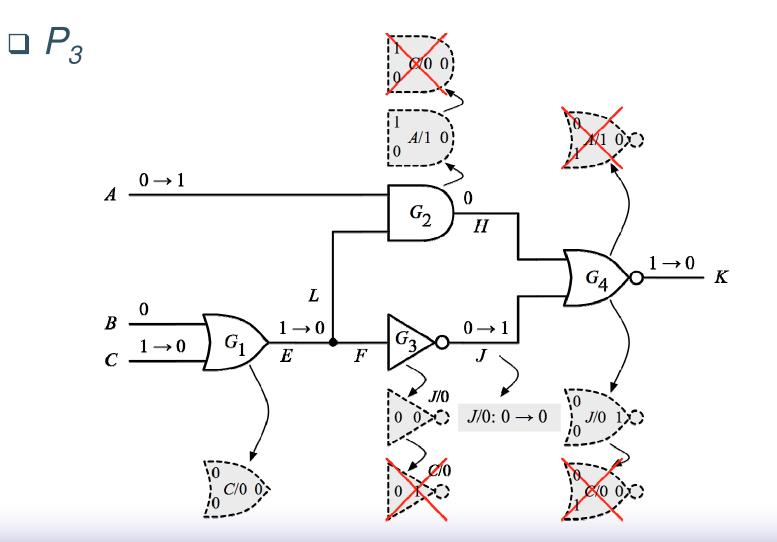

#### **Example (cont'd)**

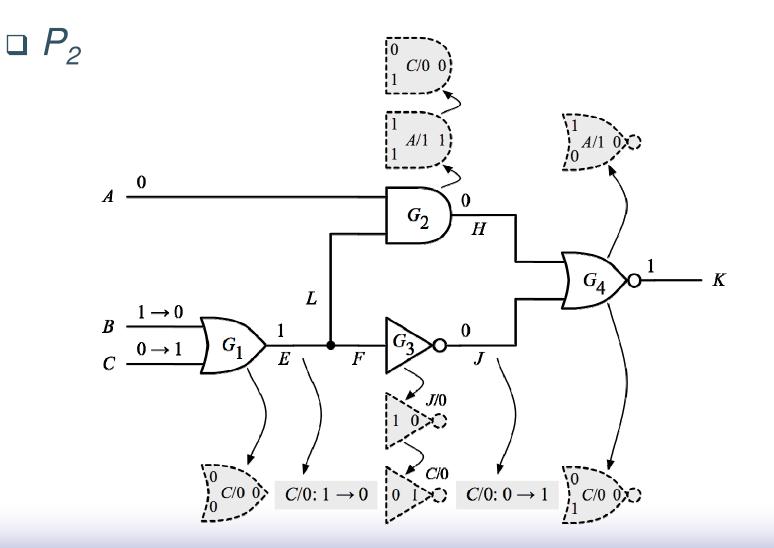

$\Box P_2$

#### **VLSI Test Principles and Architectures**

**VLSI Test Principles and Architectures**

#### **Pro and Con**

#### Advantages

- Very efficient

- Simulate all faults in one pass

#### Disadvantages

- Not easy to handle unknowns

- Only for zero-delay timing model

- Potential memory management problem

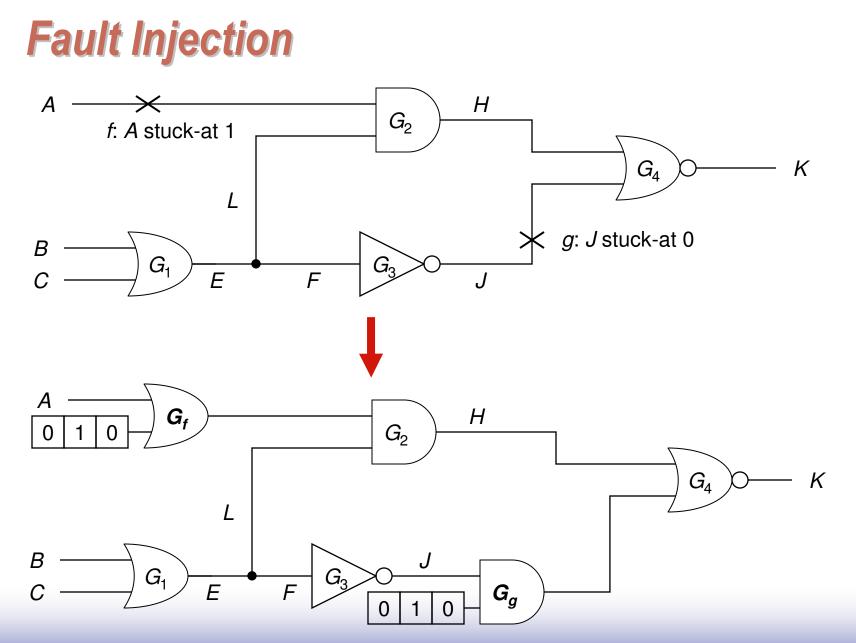

### **Concurrent Fault Simulation**

#### □ [Ulrich 1974]

- □ Simulate only differential parts of whole circuit

- Event-driven simulation with fault-free and faulty circuits simulated altogether

- Concurrent fault list for each gate

- Consist of a set of bad gates

- Fault index & associated gate I/O values

- Initially only contains local faults

- Fault propagate from previous stage

## **Good Event and Bad Event**

#### Good event

- Events that happen in good circuit

- Affect both good gates and bad gates

#### Bad event

- Events that occur in the faulty circuit of corresponding fault

- Affect only bad gates

- Diverge

- Addition of new bad gates

- Converge

- Removal of bad gates whose I/O signals are the same as corresponding good gates

VLSI Test Principles and Architectures

### **Example**

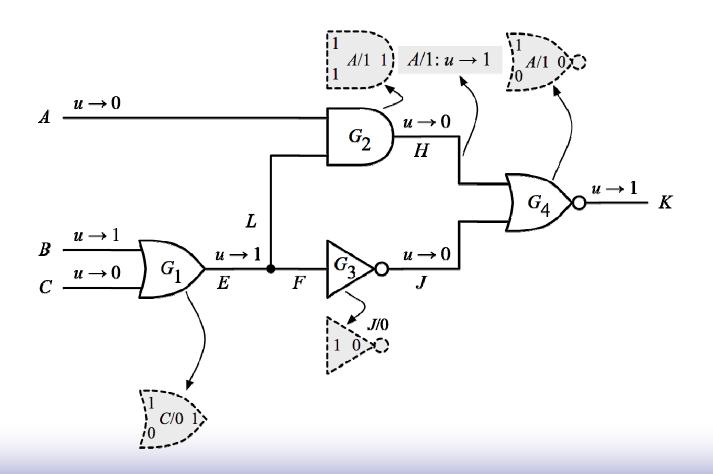

$\Box P_1$

**VLSI Test Principles and Architectures**

VLSI Test Principles and Architectures

**VLSI Test Principles and Architectures**

### **Pro and Con**

- Advantages

- Efficient

- Disadvantages

- Potential memory problem

- Size of the concurrent fault list changes at run time

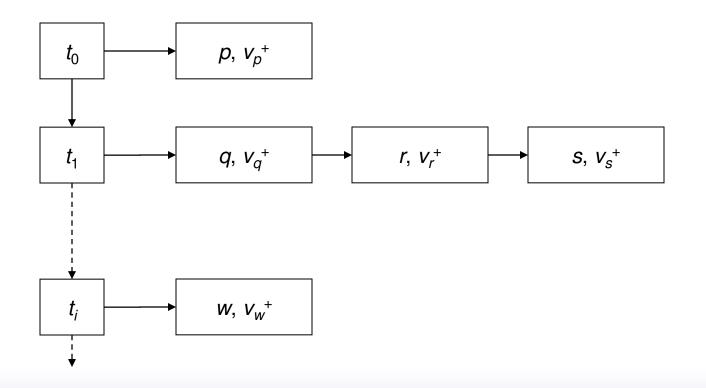

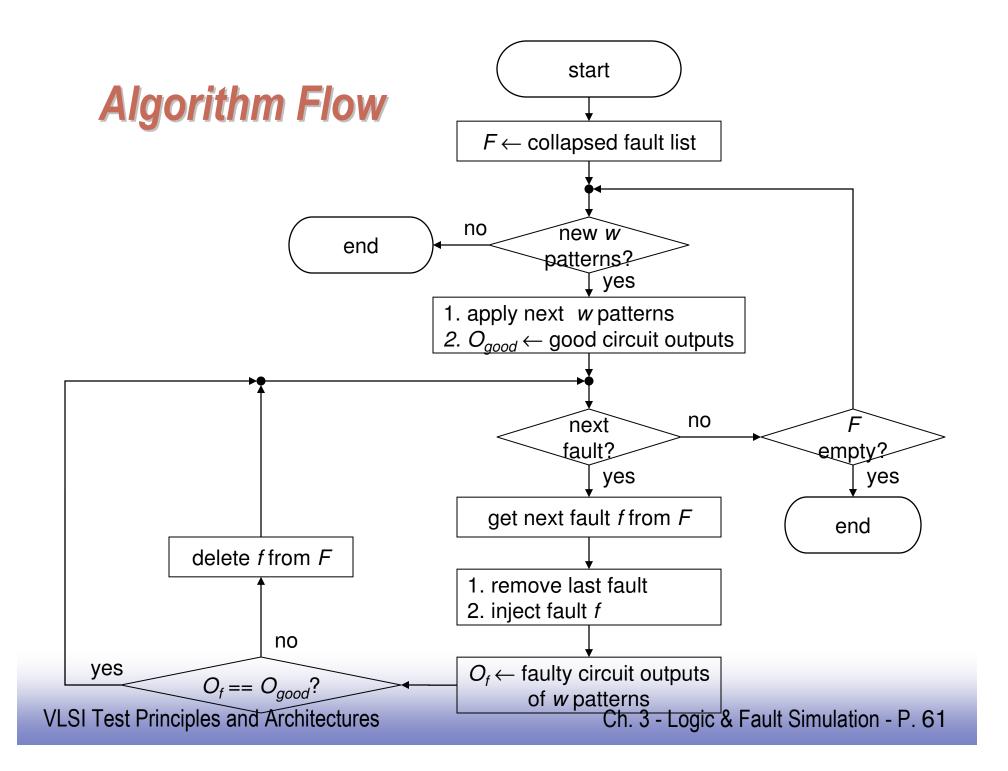

### **Differential Fault Simulation**

□ [Cheng 1989]

Combines the merits of two techniques

- Concurrent fault simulation

- PPSFP

- 🗆 Idea

- Simulate in turn every fault circuit

- Track only difference between faulty circuit and last simulated one

- Inject differences as events

- Easily implemented by event-driven simulator

### **Simulation Sequence**

|              | <i>P</i> <sub>1</sub>     | <b>P</b> <sub>2</sub>     | ••• | P <sub>i</sub>          | <i>P</i> <sub>i+1</sub>     | ••• | P <sub>n</sub>     |

|--------------|---------------------------|---------------------------|-----|-------------------------|-----------------------------|-----|--------------------|

| Good         | G <sub>1</sub>            | $G_2$                     | ••• | G <sub>i</sub>          | <i>G</i> <sub>i+1</sub>     | ••• | G <sub>n</sub>     |

| $f_1$        | <b>F</b> <sub>1,1</sub>   | <b>F</b> <sub>1,2</sub>   | ••• | F <sub>1,i</sub>        | F <sub>1,i+1</sub>          | ••• | F <sub>1,n</sub>   |

| $f_2$        | <b>F</b> <sub>2,1</sub>   | F <sub>2,2</sub>          | ••• | <b>F</b> <sub>2,i</sub> | F <sub>2,i+1</sub>          | ••• | / F <sub>2,n</sub> |

| •            | •                         | •                         |     | •                       |                             |     | •                  |

| $f_{ m k}$   | F <sub>k,1</sub>          | <b>F</b> <sub>k,2</sub>   |     | $m{F}_{k,i}$            | F <sub>k,i+1</sub>          |     | F <sub>k,n</sub>   |

| $f_{ m k+1}$ | <i>F</i> <sub>k+1,1</sub> | <i>F</i> <sub>k+1,2</sub> |     | F <sub>k+1,i</sub>      | <i>F</i> <sub>k+1,i+1</sub> |     | F <sub>k+1,n</sub> |

| •            | •                         | •                         |     | • /                     | •                           | /   | •                  |

| $f_{ m m}$   | $F_{\rm m,1}$             | F <sub>m,2</sub>          | ••• | F <sub>m,i</sub>        | F <sub>m,i+1</sub>          | ••• | F <sub>m,n</sub>   |

**VLSI Test Principles and Architectures**

### **Pro and Con**

#### Advantages

- Suitable for sequential fault simulation

- Disadvantages

- Order of events caused by faulty sites is NOT the same as the order of the timing of their occurrence

### **Fault Detection**

Hard detected fault

- Outputs of fault-free and faulty circuit are different

- 1/0 or 0/1

- No unknowns, no Z

- Potentially detected fault

- Whether the fault is detected is unclear

- Example: stuck-at-0 on enable signal of tri-state buffer

# Fault Detection (cont'd)

### Oscillation faults

- Cause circuit to oscillate

- Impossible to predict faulty circuit outputs

- Hyperactive faults

- Catastrophic fault effect

- Fault simulation is time and memory consuming

- Example: stuck-at fault on clock

- Usually counted as detected

- Save fault simulation time

# **Comparison of Fault Simulation Techniques (1)**

#### □ Speed

- Serial fault simulation: slowest

- Parallel fault simulation: O(n<sup>3</sup>), n: num of gates

- Deductive fault simulation: O(n<sup>2</sup>)

- Concurrent fault is faster than deductive fault simulation

- Differential fault simulation: even faster than concurrent fault simulation and PPSFP

#### □ Memory usage

- Serial fault simulation, parallel fault simulation: no problem

- Deductive fault simulation: dynamic allocate memory and hard to predict size

- Concurrent fault simulation: more severe than deductive fault simulation

- Differential fault simulation: less memory problem than concurrent fault simulation

# **Comparison of Fault Simulation Techniques (2)**

- □ Multi-valued fault simulation to handle unknown (X) and/or high-impedance (Z)

- Serial fault simulation, concurrent fault simulation, differential fault simulation: easy to handle

- Parallel fault simulation: difficult

- Delay and functional modeling capability

- Serial fault simulation: no problem

- Parallel fault simulation, deductive fault simulation: not capable

- Concurrent fault simulation: capable

- Differential fault simulation: capable

# **Comparison of Fault Simulation Techniques (3)**

### Sequential circuit

- Serial fault simulation, parallel fault simulation, concurrent fault simulation, differential fault simulation: no problem

- PPSFP: difficult

- Deductive fault simulation: difficult due to many unknowns

# **Comparison of Fault Simulation Techniques (4)**

- PPSFP and concurrent fault simulation are popular for combinational (full-scan) circuits

- Differential fault simulation and concurrent fault simulation is popular for sequential circuits

- Multiple-pass fault simulation

- Prevent memory explosion problem

- Distributed fault simulation

- Reduce fault simulation time

### **Alternative to Fault Simulation**

- □ Toggle Coverage

- □ Fault Sampling

- Critical Path Tracing

- Statistical Fault Analysis

# **Toggle Coverage**

- Popular for estimating fault grading

- □ Only one single fault-free simulation

- □ A net is toggled if

- Relaxed def: its value has been set to zero and one during fault-free simulation

- Stringent def: it has both a zero-to-one transition and a one-to-zero transition during fault-free simulation

- Toggle coverage

number of toggled nets number of total nets in the circuit

# **Fault Sampling**

- □ [Butler 1974]

- □ Simulate only a sampled group of faults

- Error depends on two factors

- Sample size

- The sample is biased or not

# **Critical Path Tracing**

- □ [Abramovici 1984]

- Critical value

- For net x, stuck-at v' can be detected by test pattern t ↔ Net x has critical value v

- Critical path

- Path consisting of nets with critical value

- Special attention required for fanout reconvergence

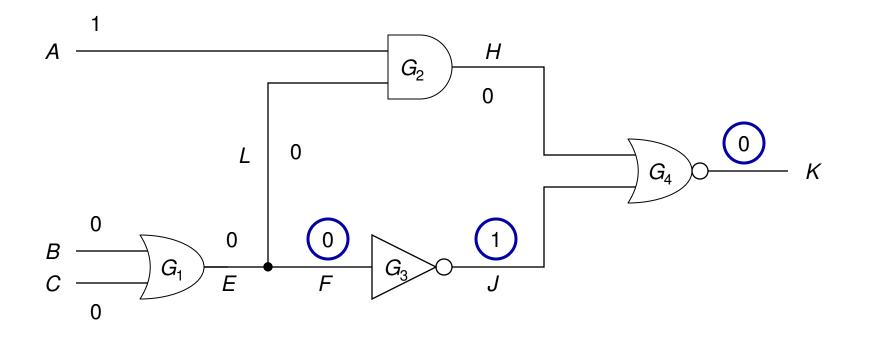

#### **Example** $\square P_1$ 0 Α Η $G_2$ 0 1 L 1 K $G_4$ 1 1 1 0 В $G_1$ $G_3$ Ε F С J 0

### **Example (cont'd)**

$\Box P_3$

Ch. 3 - Logic & Fault Simulation - P. 93

# Statistical Fault Analysis (STAFAN)

□ [Jain 1985]

Use probability theory to estimate expected value of fault coverage

$\Box$  Detectability of fault  $f(d_f)$

- 1-controllability, C1(x)

- 0-controllability, C0(x)

- Observability, O(x)

- Sensitization probability, S(x)

### **Summary**

### □ Fault simulation is very important for

- ATPG

- Diagnosis

- Fault grading

- Popular techniques

- Serial, Parallel, Deductive, Concurrent, Differential

- Requirements for fault simulation

- Fast speed, efficient memory usage, modeling functional blocks, sequential circuits

# **Logic and Fault Simulation**

- Introduction

- Simulation models

- □ Logic simulation

- Fault simulation

- □ Concluding remarks

### **Conclusions**

- Logic and fault simulations, two fundamental subjects in testing, are presented

- Into the nanometer age, advanced techniques are required to address new issues

- High performance

- High capacity

- New fault models